爲此,湖南(nán)新實網絡科技有限公司基于FPGA内部的查找表邏輯和RAM資(zī)源,設計實現了具有TCAM功能的IP核——XS-TCAM-104x320。

一(yī)、XS-TCAM-104x320的基本指标

目前實現的指标:

- 1. 編譯速率:125Mhz

- 2. 規則條數:320條

- 3. LUT資(zī)源:16799

- 4. RAM(M10K)資(zī)源:368

- 5. 查詢周期:首次單條規則查詢12周期出結果,後續連續查詢則1個時鍾周期出結果。

二、XS-TCAM-104x320的實現原理

XS-TCAM-104x320 IP,優勢如下(xià):

- 1. 支持匹配域關鍵字的按需擴展;

- 2. 支持規則條目的按需擴展;

- 3. 支持硬件進行規則更新;

- 4. 采用流水化并行的處理方式可實現高速查找匹配;

- 5. 支持規則查找/更新按掩碼匹配;

- 6. 支持按優先級查找匹配。

2.2

設計思想

XS-TCAM-104x320

IP使用二維數組的存儲方式,并行的進行規則更新及查找匹配,并采用流水化的方式實現多條規則匹配查找,從而實現高效快速的分(fēn)類查找的目的。另外(wài),此算法支持靈活的匹配域及流表表項的擴展能力,可滿足将來匹配域擴展及流表表項擴展的需求。

XS-TCAM-104x320

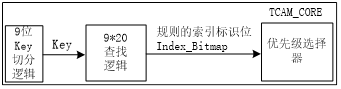

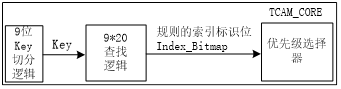

IP是基于FPGA每個内嵌RAM塊可配置成512*20的雙端口RAM進行的實現, 圖1爲XS-TCAM-104x320

IP基本處理結構圖,由于RAM塊爲512*20因此切分(fēn)的匹配域關鍵字(Key)爲9位,查找邏輯以9位Key爲查找地址對表項進行訪問,得到20位的規則索引标識位,優先級選擇器則根據優先級輸出最高優先級的規則索引。此算法将索引0位的規則定義爲最高優先級的索引位。

圖

1 XS-TCAM-104x320 IP基本處理結構圖

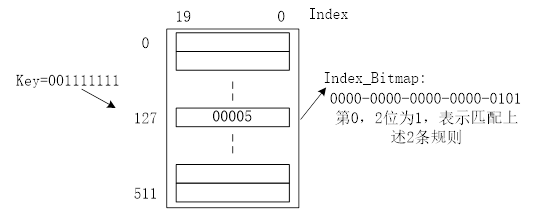

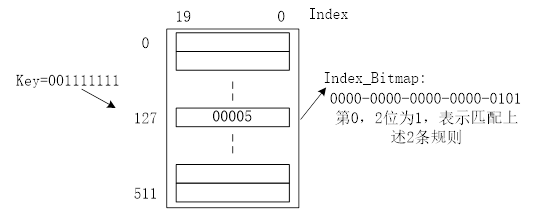

參照圖2,圖2爲流表匹配域的存儲結構圖,其爲512*20的RAM存儲塊,在此可視爲512*20的二維數組,其中(zhōng)行地址512個,爲匹配域關鍵字(Key)字段;列地址爲20個,爲規則索引字段(Index)。圖2将9位的Key作爲地址查找RAM(Key=00111_1111),查找出的結果爲此關鍵字段命中(zhōng)的20條規則的索引标識位(Index_Bitmap)爲0_0005,其中(zhōng)第0,2,位爲1,表示該key匹配了上述2條規則。由于0爲高優先級位,因此0号索引被輸出。

圖

2流表匹配域存儲結構圖

2.3

規則長度擴展

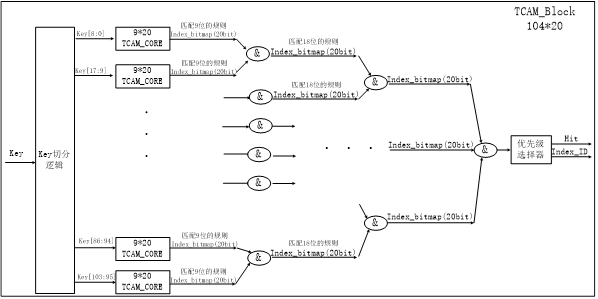

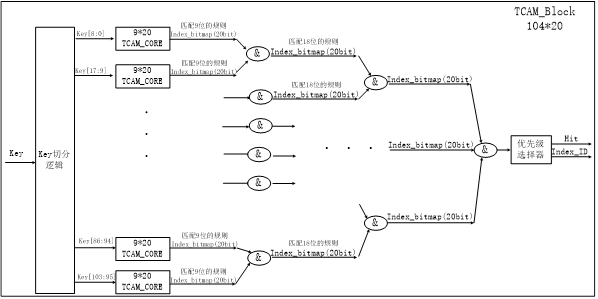

對于104位的五元組信息,需12個9*20TCAM_CORE即可實現,輸出的bitmap進行比特與即可得到匹配的bitmap,如圖3所示;

圖3

規則長度擴展到五元組處理流程圖

最後,通過優先級選擇器選擇優先級比較高的索引輸出。

2.4

規則數目擴展

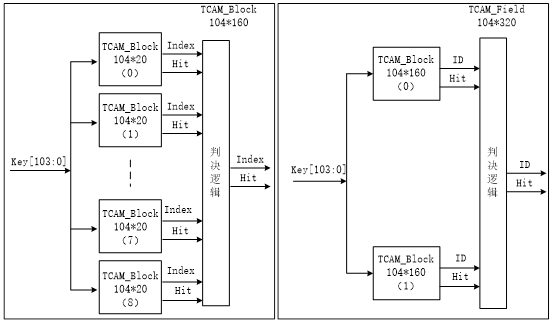

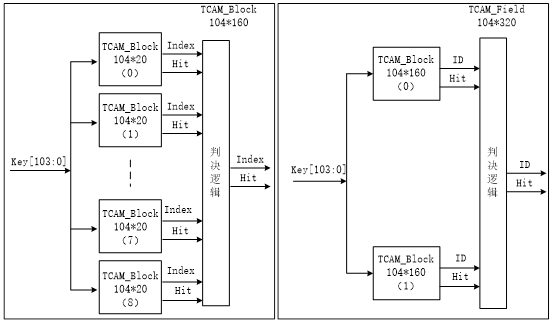

通過擴展TCAM_Block模塊可以實現規則數目的擴展,如圖4所示,通過将不同的規則對應到不同TCAM_Block模塊的Bitmap中(zhōng),則可以并行的擴展規則的數目。通過此方式在資(zī)源允許的情況下(xià)可以無限制的擴展。

圖4

規則擴展結構圖

目前基于Altera A5 FPGA

的FAST架構隻實現的320條規則,若用戶需要更多表項即可按需擴展。